USI - Universal Serial Interface (Universal Serial Interface) is actually a workpiece for hardware serial transmit and receive data. This interface is not a ready-made solution for some specific data transmission protocol, but provides a more convenient way to transfer data than in the case of full software solution.

The essence of this interface is that it offers a level of hardware to transmit and receive serial data and protocol operation logic is the responsibility of the software implementation.

Interface Register Description USI

This interface contains only four registers, which are responsible for its operation:

- USIDR - Data register

- USIBR - register for data buffering

- USISR - interface status register

- USICR - control and interface configuration register

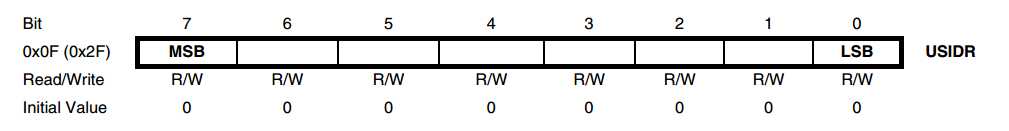

USIDR – USI Data Register

Data from this register is accessed directly, with a copy of the data can be found USIBR register. This register is used for both transmit and receive information.

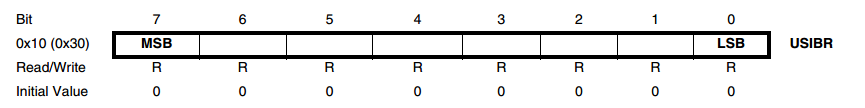

USIBR – USI Data Buffer

This register is read-only, as opposed to USIDR. This register is copied data that fall into the register USIDR when receiving information from the outside. This minimizes data loss during high load on the system of reception and transmission, as well as give time microcontroller processor time to perform the preceding tasks that he is busy.

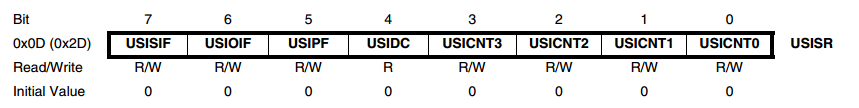

USISR – USI Status Register

USI interface status register contains the interrupt flags, flags of the status of data lines, and a counter that counts the number of bits to be transmitted in a data transmission line.

- Bit 7 - USISIF: Start Condition Interrupt Flag - Flag determining the starting premise. Used in Two-wire mode. Cleared unit record.

- Bit 6 - USIOIF: C ounter Overflow Interrupt Flag - interrupt flag overflow counter. This flag is raised when all the data bits transmitted in the transmission line. Cleared unit record.

- Bit 5 - USIPF: Stop Condition Flag - Flag determining foot parcel, which is also used in the Two-Wire mode. Remarkably, this flag is not a flag of the interrupt. Cleared unit record.

- Bit 4 - USIDC: Data Output Collision - This bit is used for master arbitration in Two-wire mode.

- Bits 3: 0 - USICNT3: 0: Counter Value - counter bits. The counter value is taken from 0 to 15 for transmitting 8 bits. The counter can be incremented by external influences, by timer or by the software switch, namely the installation of USITC bit in USICR register. As used in this article.

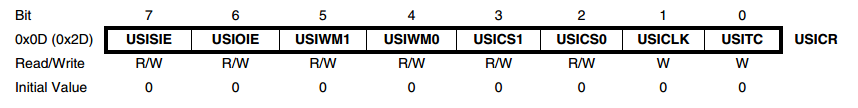

USICR – USI Control Register

Register control and customization include the interrupt enable bits, set the operation mode, count source selection of gating data.

- Bit 7 - USISIE: Start Condition Interrupt Enable - including interruption at a starting premise.

- Bit 6 - USIOIE: Counter Overflow Interrupt Enable - including overflow interrupt counter.

- Bit 5: 4 - USIWM1, USIWM0: Wire Mode - setting the data transfer mode.

- Bit 3: 2 - USICS1, USICS0: Clock Source Select - installation source bits gating counter.

- Bit 1 - USICLK: Clock Strobe - Bit strobe signal for the promotion of data link.

- Bit 0 - USITC: Toggle Clock Port Pin - If this bit is set in the unit of a change in the status of the selected pin from 0 to 1 or from 1 to 0 (which is in the Two-Wire mode, works as SCL line).

Using the USI interface

This article shows a variant of the transmission bytes of information to the target device. Promotion of bits of information is carried out by changing the SCL line state from 0 to 1. The interface itself works in the Two-Wire mode. Data is transmitted on the SDA line. Given that the counter is incremented each time the USITC bit, then to transfer 8-bit data is required 16 times to set a bit USITC, as to set up Below is an option, in which the bit is transmitted to the data line only when you change the line state from 0 to 1.

;======= The initialization routine in USI TWO-wire mode operation ========================

usi_init:

sbi PORTA,4 ; Is reset PORT SCL

sbi PORTA,6 ; Is reset PORT SDA

sbi DDRA,4 ; Is reset DDR SCL

sbi DDRA,6 ; Is reset DDR SDA

ldi r16,0xFF

out USIDR,r16

ldi r16,(0<<USISIE)|(0<<USIOIE)|(1<<USIWM1)|(0<<USIWM0)|(1<<USICS1)|(0<<USICS0)|(1<<USICLK)|(0<<USITC)

; (0<<USISIE)|(0<<USIOIE) Disable interrupts on the counter and the start

; (1<<USIWM1)|(0<<USIWM0) Install the two-wire mode

; (1<<USICS1)|(0<<USICS0)|(1<<USICLK) Counter mode setting

; bit is transmitted by changing the SCL line state from 0 to 1

; (0<<USITC) the initial state of the output clock signal

out USICR,r16 ; Submitting byte received in USICR

ldi r16,(1<<USISIF)|(1<<USIOIF)|(1<<USIPF)|(1<<USIDC)|(0x0<<USICNT0) ; Cleaning the flags and the counter is reset

out USISR,r16 ;Submitting byte received in USISR

ret

;======= Sending information via the USI byte interface =================================

usi_send:

out USIDR,r16 ; Loading data to USIDR

ldi r16,0xF0 ; Installing USISR counter to transfer 8 bits of data

out USISR,r16 ; Submitting byte received in USISR

ldi r16,(0<<USISIE)|(0<<USIOIE)|(1<<USIWM1)|(0<<USIWM0)|(1<<USICS1)|(0<<USICS0)|(1<<USICLK)|(1<<USITC)

; (0<<USISIE)|(0<<USIOIE) Disable interrupts on the counter and the start

; (1<<USIWM1)|(0<<USIWM0) Install the two-wire mode

; (1<<USICS1)|(0<<USICS0)|(1<<USICLK) Counter mode setting

; (1<<USITC) the initial state of the output clock signal

transfer:

out USICR,r16 ; Submitting byte received in USICR

out USICR,r16 ; Submitting byte received in USICR

in r17,USISR

sbrs r17,6

rjmp transfer

ldi r16,(1<<USISIF)|(1<<USIOIF)|(1<<USIPF)|(1<<USIDC)|(0x0<<USICNT0) ; Cleaning flags

out USISR,r16 ; Submitting byte received in USISR

ret

;========================================================================================