Microcontrollers AVR Atmega48 / 88/168/328 contain the EEPROM memory of 256/512/512 / 1K bytes , respectively. EEPROM in AVR microcontrollers can support up to 100,000 write cycles. Access to non-volatile memory is carried out through three types of registers:

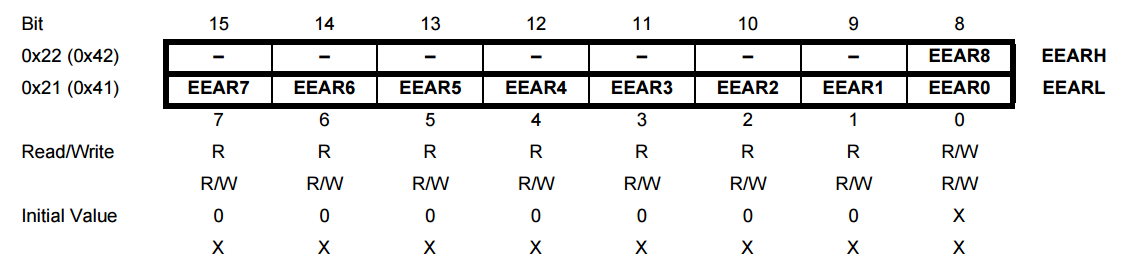

- EEARH, EEARL - registers the addressing of memory cells. In case Atmega48 EEARH absent, because in this type of microcontroller 256 is present in all memory cells. EEARH responsible for the high byte of memory address, EEARL for the least significant byte;

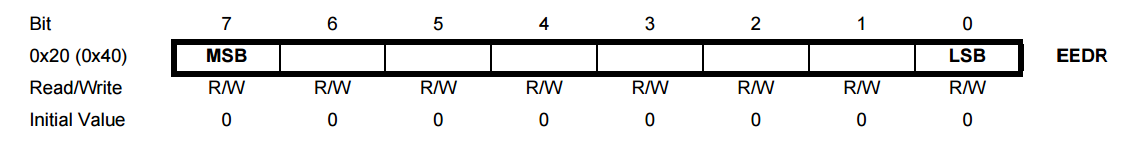

- EEDR - register for writing and reading data;

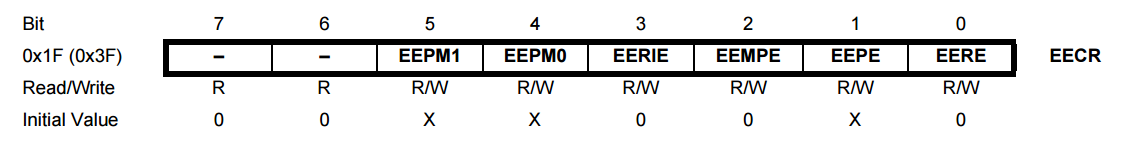

- EECR - register control, this register is setting the actions to be performed with the memory.

A detailed description of EEPROM registers

EEARH and EEARL - registers EEPROM cell address

Bits from 9 to 15 are reserved and always read with the value zero.

Bits from 0 to 8 are used to indicate non EEPROM memory cell to which the treatment will be.

EEDR - EEPROM data register

Bits from 2 to 7 - which is written bits in the information to be recorded in EEPROM or read from it.

Bits from 6 to 7 - bits are reserved

Bits from 4 to 5 - EEPM1 and EEPM0 - EEPROM used to set the operation mode.

- EEPM1 = 0, EEPM0 = 0 - An atomic operation is the removal and recording of data (duration 3.4 ms)

- EEPM1 = 0, EEPM0 = 1 - Only the deletion of data (duration 1.8 ms)

- EEPM1 = 1, EEPM0 = 0 - Data Entry Only (duration 1.8 ms)

- EEPM1 = 1, EEPM0 = 1 - Reserved for future use

Bit 3 - EERIE - this bit is used to enable interrupts, in case if you are allowed to interrupt the firmware of your controller.

Bit 2 - EEMPE - protection bit of the recording. Delays process of writing data to the EEPROM on the four cycles to EEPROM had time to prepare for the recording of data.

Bit 1 - EEPE - write bit start, exhibited to start recording, cleared to zero in hardware, at a time when the recording is completed. Therefore, it may be used to control the data recording process in EEPROM.

Bit 0 - WERE - bit start reading. exhibit for reading from EEPROM launch.

Read and write operations

Atmega EEPROM in a very slow interface, which requires up to 4 ms to perform write operations. Therefore it is very important to check that the previous write operation is completed successfully.

;======= EEPROM write procedure in ======================================================

EEWrite:

sbic EECR,EEPE ; We expect that over the previous write operation.

rjmp EEWrite ; Out of the loop as long as the flag is cleared EEPE

cli ; Then we put out a ban on interrupting.

out EEARL,r16 ; Set the address of the cell to which we refer

out EEDR,r17 ; as well as write data to the register information,

; that will keep

sbi EECR,EEMPE ; set protection on record

sbi EECR,EEPE ; set the write flag

sei ; then allow interrupt

ret ; and return from the subroutine.

;======= The procedure of reading from the EEPROM ======================================

EERead:

sbic EECR,EEPE ; We expect that over the previous write operation.

rjmp EERead

out EEARL, r16 ; Set the address of the cell to which we refer

sbi EECR,EERE ; Start reading setting for reading the flag

in r17, EEDR ; Return the reading result in the desired register

ret

;=======================================================================================